# Real-time Processor Architectures for Worst Case Execution Time Reduction

(Submitted for the degree of Doctor of Philosophy)

Jack Whitham

Department of Computer Science, University of York

January 2008

# Abstract

In a real-time system, programs must respond to external events in a timely fashion, completing all required subtasks before a deadline elapses. Worst case execution time (WCET) analysis is used to assure that deadlines are always met by determining the maximum period of time required to execute parts of a program. WCET analysis has been extensively studied, but existing techniques do not work well with CPUs that make use of dynamic execution optimisation features such as caches and superscalar out-of-order issue units. These features work well for average case execution time (ACET) reduction, but not for WCET reduction, since software must model the worst possible behaviour of the dynamic features to find the WCET.

This thesis explores the architectural issues relating to these problems, then characterises a class of CPU architecture that is explicitly designed for WCET reduction. An implementation of this architecture enables WCET reduction by allowing programs to move worst-case execution paths into a microprogram store, which acts as an scratchpad for parallel microinstructions. The exploitation of instruction-level parallelism (ILP) across basic block boundaries is enabled by the use of a superblock scheduler, which allows the architecture to reduce WCET further than previous CPU architectures intended to facilitate timing analysis.

Instances of the new architecture class are implemented and tested using field-programmable gate array (FPGA) hardware. A WCET reduction algorithm is proposed, implemented and tested based on the implicit path enumeration technique (IPET) for WCET analysis. Experiments are used to compare the algorithm and architecture with previous work.

# **Table of Contents**

| 1 | Intr | oductio | n                                                   | 1  |

|---|------|---------|-----------------------------------------------------|----|

|   | 1.1  | Thesis  | Aims                                                | 3  |

|   | 1.2  | Digital | Appendix                                            | 4  |

|   | 1.3  | Thesis  | Structure                                           | 4  |

| 2 | Lite | rature  |                                                     | 5  |

|   | 2.1  | About   | Timing Analysis                                     | 5  |

|   |      | 2.1.1   | WCET Estimation                                     | 6  |

|   |      | 2.1.2   | Reducing Pessimism in WCET analysis                 | 8  |

|   |      | 2.1.3   | The Translation Step                                | 11 |

|   |      | 2.1.4   | CPU Modelling                                       | 11 |

|   | 2.2  | A Brie  | f History of CPU Technology                         | 12 |

|   |      | 2.2.1   | The Memory Bottleneck                               | 12 |

|   |      | 2.2.2   | The Instruction Rate Bottleneck                     | 15 |

|   |      | 2.2.3   | Effects of Dynamic Features                         | 20 |

|   | 2.3  | WCET    | Analysis of a Complex CPU                           | 20 |

|   |      | 2.3.1   | Modelling a Pipeline in Isolation                   | 21 |

|   |      | 2.3.2   | Modelling an Instruction Cache in Isolation         | 21 |

|   |      | 2.3.3   | Modelling Pipelines and Instruction Caches Together | 24 |

|   |      | 2.3.4   | Modelling Multiple-Issue Pipelines                  | 25 |

|   |      | 2.3.5   | Modelling Branch Prediction                         | 25 |

|   |      | 2.3.6   | Practical Issues for CPU Modelling                  | 26 |

|   |      | 2.3.7   | Timing Anomalies                                    | 28 |

|   |      | 2.3.8   | Accounting for Timing Anomalies                     | 30 |

|   |      | 2.3.9   | Trends Leading Away From Complex Models             | 30 |

|   |      | 2.3.10  | Alternative Implementation Platforms                | 32 |

|   |      | 2.3.11  | Statistical Analysis Methods                        | 34 |

|   |      | 2.3.12  | Multitasking                                        | 35 |

|   |      | 2.3.13  | Summary                                             | 36 |

|   | 2.4  | Improv  | ving Worst-Case Performance Using Software          | 37 |

|   |      | 2.4.1   | Manual Optimisation                                 | 38 |

|   |      | 2.4.2   | Automatic Optimisation                              | 40 |

|   |      | 2.4.3   | Manual Run-time Specialisation                      | 43 |

|   |      | 2.4.4   | Summary                                             | 44 |

|   | 2.5  | Applic  | ation-Specific Hardware                             | 44 |

|   |      | 2.5.1   | Hardware Description Languages                      | 45 |

|   |      | 2.5.2     | ASICs and FPGAs 45                                    |

|---|------|-----------|-------------------------------------------------------|

|   |      | 2.5.3     | Summary                                               |

|   | 2.6  | Improv    | ring Worst-Case Performance Using Hardware            |

|   |      | 2.6.1     | Co-processors                                         |

|   |      | 2.6.2     | Application-Specific Instruction Processors (ASIPs)50 |

|   |      | 2.6.3     | ASIP Techniques                                       |

|   |      | 2.6.4     | Classical Co-design                                   |

|   |      | 2.6.5     | Using FPGA-based Run-time Reconfiguration             |

|   |      | 2.6.6     | Coarse-Grained Reconfigurable Architectures           |

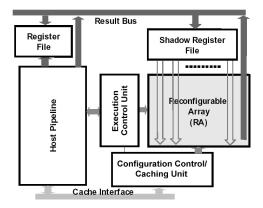

|   |      | 2.6.7     | CGRAs within a CPU Core                               |

|   |      | 2.6.8     | Compiling Code for an RFU                             |

|   | 2.7  | Summa     | ary                                                   |

| 3 | Mot  | ivation a | and Hypothesis 73                                     |

|   | 3.1  | Revise    | d Thesis Aims                                         |

|   | 3.2  | Statem    | ent Of Requirements                                   |

|   | 3.3  | Approa    | ach                                                   |

|   | 3.4  | Hypoth    | nesis                                                 |

|   | 3.5  | Evalua    | tion Criteria                                         |

| 4 | Arcl | hitectur  | e 79                                                  |

|   | 4.1  | Introdu   | cing TARGET and the WCET Reduction Process            |

|   | 4.2  | Constru   | uction of TARGET Architecture                         |

|   |      | 4.2.1     | Starting Point - CPU                                  |

|   |      | 4.2.2     | A Simple CPU, plus an RFU                             |

|   |      | 4.2.3     | Communications Infrastructure                         |

|   |      | 4.2.4     | Controlling CPU Operations                            |

|   |      | 4.2.5     | TARGET Architecture Characterisation    87            |

|   | 4.3  | Theore    | tical Evaluation                                      |

|   |      | 4.3.1     | Full Support For General Software Programs    90      |

|   |      | 4.3.2     | Basic Block Timing Invariance                         |

|   |      | 4.3.3     | Efficient Optimisation Process                        |

|   |      | 4.3.4     | Scalability                                           |

|   |      | 4.3.5     | WCET Reduction versus Previous Work                   |

|   |      | 4.3.6     | TARGET Bottleneck    92                               |

|   |      | 4.3.7     | Summary                                               |

| 5 | Stat | ic Imple  | ementation 95                                         |

|   | 5.1  | Simula    | tion                                                  |

|   |      | 5.1.1     | Existing Simulators                                   |

|   |      | 5.1.2     | Simulator Validation                                  |

|   |      | 5.1.3     | Simulating an RFU                                     |

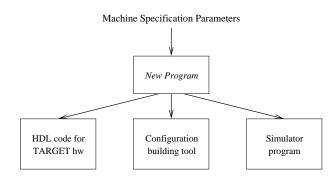

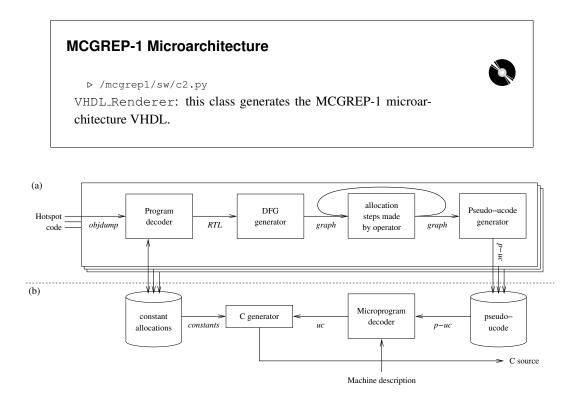

|   | 5.2  | MCGR      | EP-1 TARGET Generator    99                           |

|   |      | 5.2.1     | Parameterisable Features                              |

|   |      | 5.2.2     | Non-Parameterisable Features                          |

|   |      | 5.2.3     | Microarchitecture                                     |

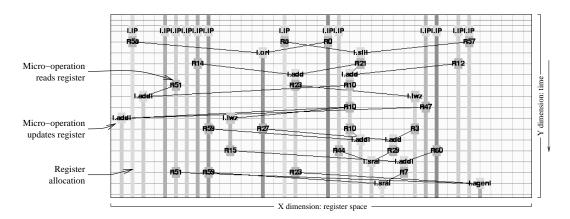

|      | 5.2.4     | Microcode Generator                                  | 111 |

|------|-----------|------------------------------------------------------|-----|

|      | 5.2.5     | Simulator                                            | 114 |

| 5.3  | MCGR      | EP-1 Evaluation                                      | 114 |

|      | 5.3.1     | Evaluation for Correctness                           | 116 |

|      | 5.3.2     | Evaluation against the TARGET parameters             | 118 |

|      | 5.3.3     | Evaluation against the Requirements                  | 119 |

|      | 5.3.4     | Invariant basic block execution times - calculations | 119 |

|      | 5.3.5     | Invariant basic block execution times - experiment   | 121 |

|      | 5.3.6     | WCET Reduction versus Previous Work                  | 126 |

|      | 5.3.7     | Other Requirements                                   | 129 |

|      | 5.3.8     | Summary                                              | 131 |

| Exte | ensible I | mplementation                                        | 133 |

| 6.1  | Autom     | atic Microcode Generation Methods for TARGET         | 133 |

|      | 6.1.1     | Generating VLIW Code                                 | 135 |

|      | 6.1.2     | Acyclic Scheduling                                   | 136 |

|      | 6.1.3     | Cyclic Scheduling                                    | 144 |

|      | 6.1.4     | Using VLIW Scheduling Algorithms for TARGET          | 145 |

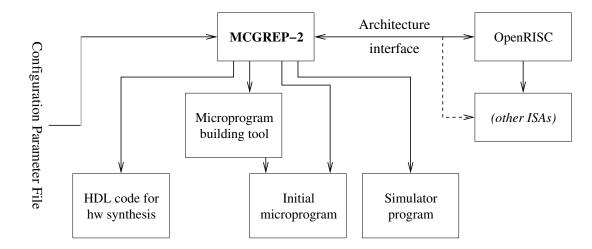

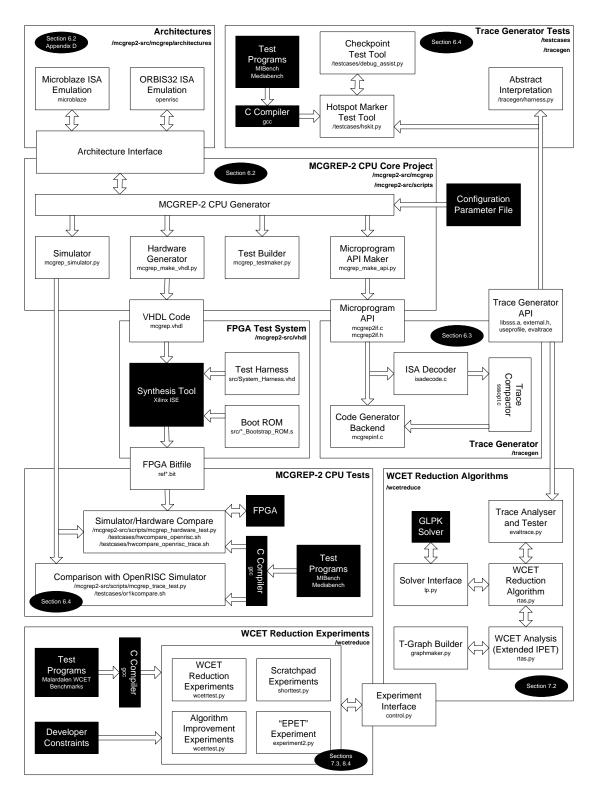

| 6.2  | MCGR      | EP-2 TARGET Generator                                | 145 |

|      | 6.2.1     | Features                                             | 146 |

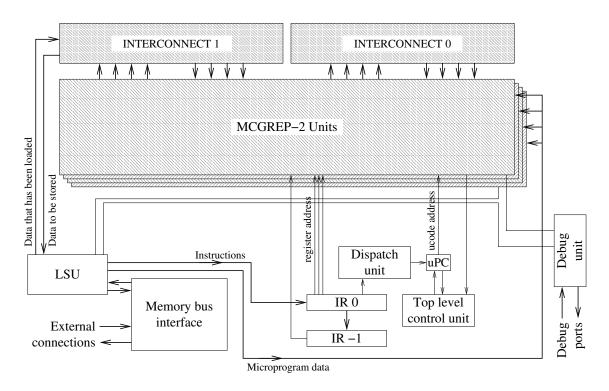

|      | 6.2.2     | Microarchitecture - Top Level                        | 150 |

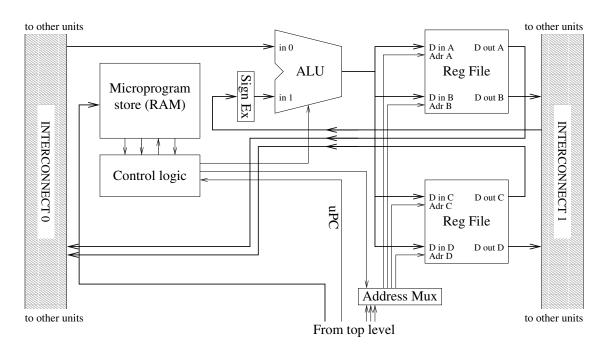

|      | 6.2.3     | Microarchitecture - Unit Level                       | 154 |

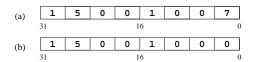

|      | 6.2.4     | Microarchitecture - Programming Interface            | 156 |

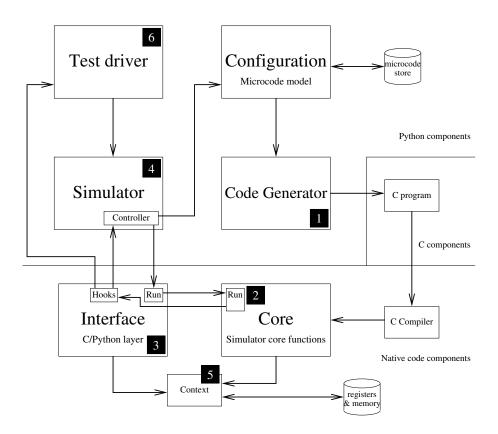

|      | 6.2.5     | Simulator                                            | 158 |

| 6.3  | MCGR      | EP-2 Trace-style Scheduler                           | 160 |

|      | 6.3.1     | Trace Formation                                      | 161 |

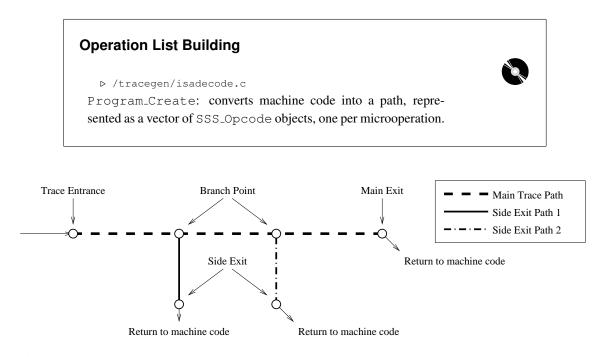

|      | 6.3.2     | Operation List Building                              | 163 |

|      | 6.3.3     | Compaction                                           | 164 |

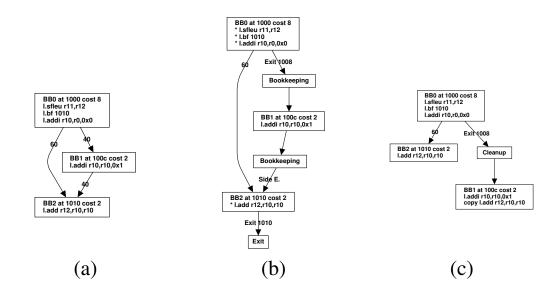

|      | 6.3.4     | Bookkeeping and Exit Cleanup                         | 168 |

|      | 6.3.5     | Output Stage                                         | 168 |

| 6.4  | MCGR      | EP-2 Evaluation                                      | 170 |

|      | 6.4.1     | Correctness Evaluation: Machine Code Operation       | 170 |

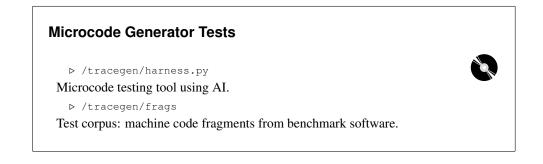

|      | 6.4.2     | Correctness Evaluation: Microcode Generator          | 172 |

|      | 6.4.3     | Correctness Evaluation: Machine Code and Microcode   | 174 |

|      | 6.4.4     | Correctness Evaluation: Microcode in Hardware        | 178 |

|      | 6.4.5     | Evaluation against the TARGET parameters             | 178 |

|      | 6.4.6     | Evaluation against the Requirements                  | 180 |

|      | 6.4.7     | Invariant basic block execution times                | 180 |

|      | 6.4.8     | WCET Reduction versus Previous Work                  | 181 |

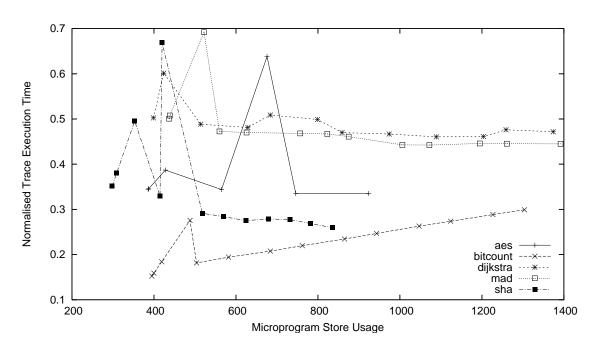

|      | 6.4.9     | Efficient optimisation process                       | 184 |

|      | 6.4.10    | Scalability - programs of any size                   | 185 |

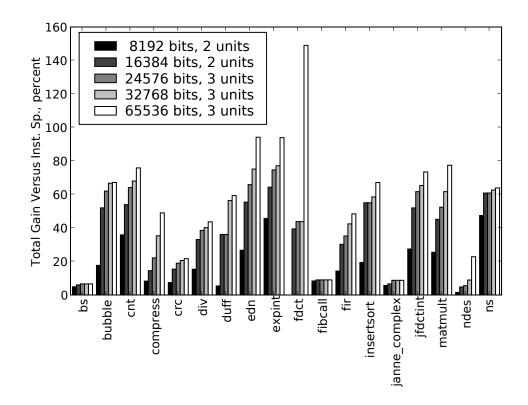

|      | 6.4.11    | Scalability - increasing resources                   | 188 |

|      | 6.4.12    | Usage of FPGA Space                                  | 190 |

|      | 6.4.13    | Optimisation Possibilities                           | 192 |

|      | 6.4.14    | Summary                                              | 195 |

| 7 | WC  | ET Red   | uction using IPET                                                       | 197  |

|---|-----|----------|-------------------------------------------------------------------------|------|

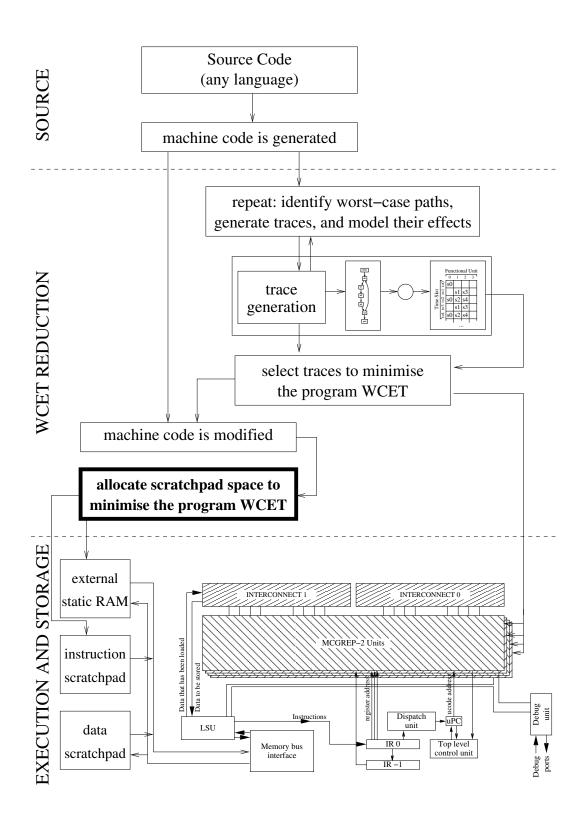

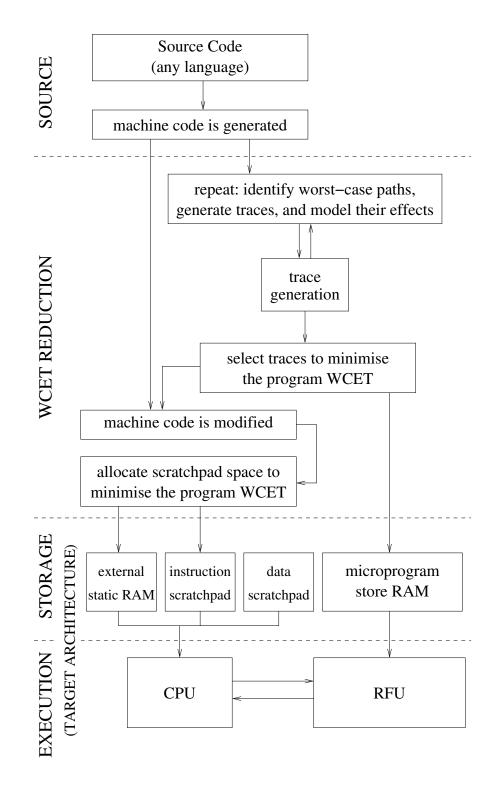

|   | 7.1 | WCET     | Reduction                                                               | 197  |

|   |     | 7.1.1    | Identifying Worst-Case Paths                                            | 201  |

|   |     | 7.1.2    | Modelling the Effects of a WCET Reduction                               | 202  |

|   |     | 7.1.3    | Modelling the Functionality of a Trace                                  | 202  |

|   |     | 7.1.4    | Modelling Worst-Case Flow of Traces                                     | 203  |

|   |     | 7.1.5    | Multiple Traces and the WCET                                            | 205  |

|   |     | 7.1.6    | Constraints                                                             | 205  |

|   |     | 7.1.7    | Equivalence to the Puschner and Schedl model                            | 205  |

|   |     | 7.1.8    | Adapting the Puschner and Schedl proof                                  | 206  |

|   |     | 7.1.9    | Allocating the Microprogram Store Space                                 | 206  |

|   |     | 7.1.10   | Microprogram Store Space Allocation Algorithm                           | 208  |

|   |     | 7.1.11   | Phase 1: Selecting Good Microprogram Starting Points and Evaluating Mi- |      |

|   |     |          | croprograms                                                             | 208  |

|   |     | 7.1.12   | Phase 2: Selecting Microprograms                                        | 212  |

|   |     | 7.1.13   | Summary                                                                 | 213  |

|   | 7.2 | Implen   | nenting and Testing the WCET Reduction Approach                         | 213  |

|   |     | 7.2.1    | Obtaining the T-graph                                                   | 213  |

|   |     | 7.2.2    | Custom Microcode-Aware WCET Analysis using IPET                         | 214  |

|   |     | 7.2.3    | Solving the Integer Linear Program                                      | 216  |

|   |     | 7.2.4    | Finding Candidates                                                      | 217  |

|   |     | 7.2.5    | Microprogram Selection                                                  | 217  |

|   |     | 7.2.6    | Testing the Implementation                                              | 218  |

|   |     | 7.2.7    | Global tests                                                            | 219  |

|   |     | 7.2.8    | Local tests                                                             | 223  |

|   |     | 7.2.9    | Explicit Path Enumeration Tests                                         | 224  |

|   |     | 7.2.10   | Summary                                                                 | 227  |

|   | 7.3 | Effectiv | veness of the WCET Reduction Algorithm                                  | 227  |

|   |     | 7.3.1    | Maximum Path Length $L$ , and Microprogram Store Space $C_{max}$        | 228  |

|   |     | 7.3.2    | Maximum Number of Search Iterations, $H$                                | 228  |

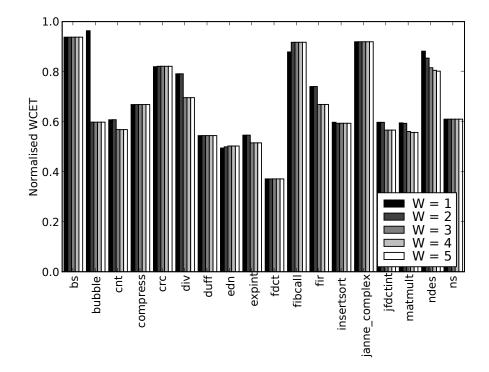

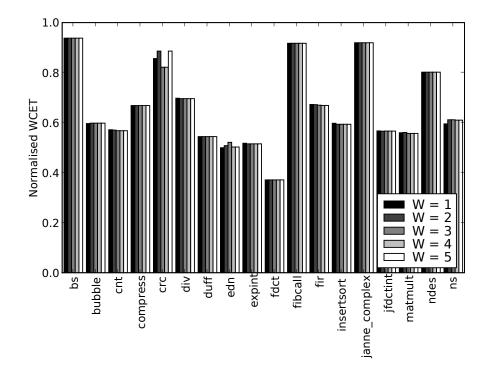

|   |     | 7.3.3    | Number of Trace Start Points to Test, $W$                               | 230  |

|   |     | 7.3.4    | Assumptions                                                             | 232  |

|   |     | 7.3.5    | Improvements: Search Strategy                                           | 234  |

|   |     | 7.3.6    | Improvements: Score Heuristic                                           | 235  |

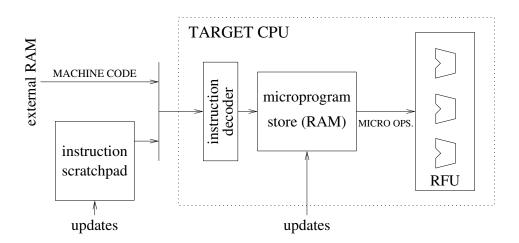

|   | 7.4 | Implen   | nenting Scratchpad Allocation                                           | 237  |

|   |     | 7.4.1    | Implementing Suhendra's Instruction Scratchpad Allocation Algorithm     | 238  |

|   | 7.5 | Summa    | ary                                                                     | 239  |

| 0 | БТ  |          |                                                                         | 0.41 |

| 8 |     | uation   |                                                                         | 241  |

|   | 8.1 | -        | ting ILP Within a Single Basic Block                                    |      |

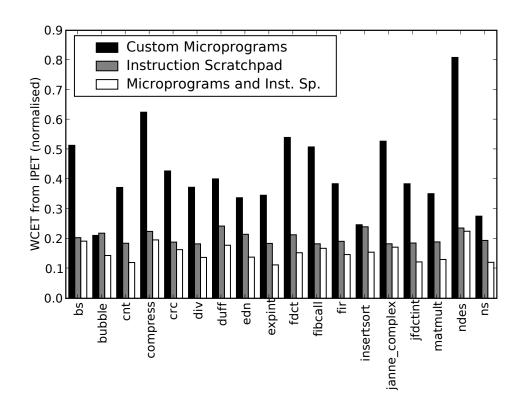

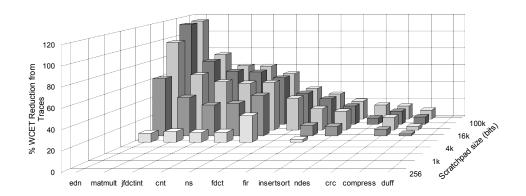

|   | 8.2 | _        | rison with Instruction Scratchpads                                      |      |

|   | 8.3 | -        | rison Experiment                                                        |      |

|   | 8.4 |          | onal Experiments                                                        |      |

|   | 8.5 | Summa    | ary                                                                     | 249  |

| 9  | Conclusion                                            | 251 |

|----|-------------------------------------------------------|-----|

|    | 9.1 Summary of Findings                               | 251 |

|    | 9.2 Future Work                                       | 253 |

|    | 9.3 Conclusion                                        | 255 |

| 10 | References                                            | 257 |

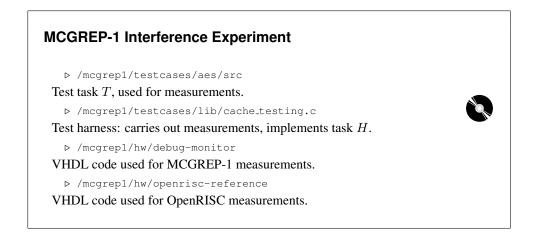

| A  | Digital Appendix Documentation                        | 277 |

|    | A.1 Overview                                          | 277 |

|    | A.2 Required/recommended Software Environment         | 279 |

|    | A.3 Installing the Archive Software                   | 280 |

|    | A.4 Building the MCGREP-1 Test Cases                  | 281 |

|    | A.5 Using the MCGREP-1 Hardware Generator             | 283 |

|    | A.6 Using the MCGREP-1 Simulator                      | 283 |

|    | A.7 Using the MCGREP-2 Test Cases                     | 284 |

|    | A.8 Using the MCGREP-2 Hardware Generator             | 284 |

|    | A.9 Using the MCGREP-2 Simulator                      | 287 |

|    | A.10 Extending MCGREP-2                               | 287 |

|    | A.11 Connecting an FPGA                               | 288 |

|    | A.12 Appendix Software Tests                          | 289 |

|    | A.13 Third Party Software and Hardware                | 289 |

| B  | Experimental Data and Test Examples                   | 291 |

| С  | OpenRISC ORBIS32 Quick Reference                      | 295 |

| D  | Microblaze Extensions for MCGREP-2                    | 299 |

|    | D.1 ALU Features                                      | 300 |

|    | D.2 ISA and Built-in Microprogram                     | 301 |

|    | D.3 Interrupt and Status Register Support             | 301 |

|    | D.4 Trace-style Scheduler                             | 302 |

|    | D.5 Repeating Experiments and Tests                   | 302 |

|    | D.6 Booting uClinux                                   | 303 |

| Е  | Implicit Path Enumeration Technique - Example         | 307 |

| F  | WCET Reduction Algorithm - Example                    | 311 |

| G  | Partitioning Support for the WCET Reduction Algorithm | 313 |

|    | G.1 Adding Partitioning Support For Microprograms     | 313 |

|    | C.2. An Automatic Dertitioning Strategy               | 314 |

|    | G.2 An Automatic Partitioning Strategy                | 514 |

# **List of Tables**

| 2.1  | Examples of IDL statements                                   | 9  |

|------|--------------------------------------------------------------|----|

| 2.2  | Puschner's integer linear programming model                  | 10 |

| 2.3  | Example CISC-style instructions                              | 15 |

| 2.4  | Li's cache-aware integer linear programming model            | 23 |

| 2.5  | Healy's hazard model                                         | 25 |

| 2.6  | FPGA and MPGA comparison                                     | 48 |

| 2.7  | The scale of classical co-design systems.                    | 53 |

| 2.8  | Examples of penalties incurred by crossing level boundaries. | 69 |

| 4.1  | The parameters of the architecture                           | 88 |

| 5.1  | Properties that are hard to evaluate without a model         | 95 |

| 5.2  | SimpleScalar tools                                           | 98 |

| 5.3  | Functional groups in the OpenRISC ORBIS32 ISA                | 03 |

| 5.4  | Special microprograms for CPUs generated by MCGREP-1         | 04 |

| 5.5  | Parameters for initial generator implementation              | 05 |

| 5.6  | Types of sign extension required by OpenRISC ORBIS32 ISA     | 07 |

| 5.7  | Types of ALU operation required by OpenRISC ORBIS32 ISA      | 07 |

| 5.8  | uPC branch commands                                          | 11 |

| 5.9  | Benchmarks                                                   | 17 |

| 5.10 | Instruction timings                                          | 20 |

| 5.11 | Least-squares derivation of unknowns                         | 25 |

| 5.12 | Number of instructions executed for each benchmark           | 27 |

| 5.13 | IPC for each CPU                                             | 28 |

| 5.14 | Core size and speed comparison                               | 30 |

|      |                                                              |    |

| 6.1  | Exceptions that may be raised 1                              |    |

| 6.2  | Parameters for MCGREP-2 generator implementation             |    |

| 6.3  | Special microprograms for CPUs generated by MCGREP-2         |    |

| 6.4  | uPC branch commands                                          |    |

| 6.5  | Types of hook provided by the MCGREP-2 simulator             |    |

| 6.6  | Benchmarks                                                   |    |

| 6.7  |                                                              | 77 |

| 6.8  | C                                                            | 80 |

| 6.9  | L                                                            | 84 |

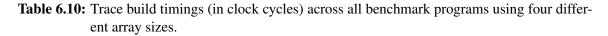

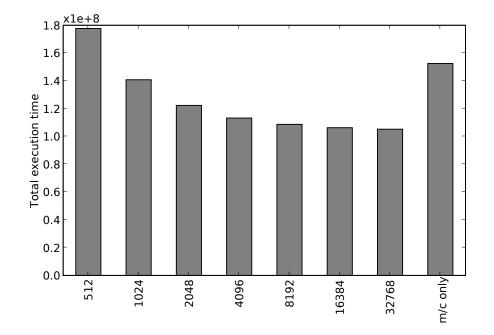

|      | Trace build timings                                          |    |

| 6.11 | Core size and speed comparison                               | 91 |

| 6.12        | No System Cycle                                              | 193 |

|-------------|--------------------------------------------------------------|-----|

| 7.1         | WCET reduction parameters                                    | 218 |

| 7.2         | Test programs for WCET reduction.                            | 219 |

| 7.3         | Global test results 1                                        | 221 |

| 7.4         | Global test results 2                                        | 222 |

| 7.5         | "EPET" Results, 2                                            | 226 |

| 7.6         | Evaluating assumptions                                       | 233 |

| 7.7         | WCET reductions with different trace lengths                 | 234 |

| 8.1         | Architectural Configuration                                  | 244 |

| 8.2         | Parameters used for the experiment described in section 8.3. | 245 |

| 8.3         | Detailed results for section 8.3                             | 246 |

| A.1         | Configuration Parameters                                     | 286 |

| <b>B</b> .1 | Results of interference experiment                           | 292 |

| B.2         | Benchmark execution times                                    | 292 |

| B.3         | Benchmark execution times                                    |     |

| B.4         | Multiple context timings                                     | 293 |

| B.5         | Improvements with different architectures                    | 294 |

| D.1         | Microblaze addition and subtraction instructions             | 300 |

| D.2         | Irregular instructions                                       | 301 |

| D.3         | Petalinux memory map                                         | 305 |

| E.1         | Execution Time Costs                                         | 308 |

| E.2         | Conservation of Flow Constraints                             | 310 |

| E.3         | Worst-case Flow Values                                       | 310 |

| F.1         | Possible trace starting points                               | 312 |

| F.2         | Execution Costs                                              | 312 |

| F.3         | WCET Reductions from BB5                                     | 312 |

| G.1         | Optimal region count for environment 1                       | 318 |

| G.2         | Optimal region count for environment 2                       | 319 |

# **List of Figures**

| 2.1  | WCET Problem Domains                                     | 7  |

|------|----------------------------------------------------------|----|

| 2.2  | Sample execution path graph                              | 7  |

| 2.3  | Infeasible path example                                  | 8  |

| 2.4  | Example: annotations used to bound WCET analysis         | 9  |

| 2.5  | CPU core frequencies: 1980-2005                          | 13 |

| 2.6  | Example of ILP                                           | 16 |

| 2.7  | Arnold's WCET approach                                   | 22 |

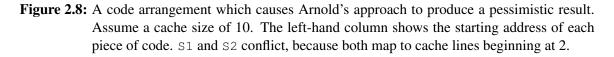

| 2.8  | Example of conservative behaviour in Arnold's approach   | 23 |

| 2.9  | Suhendra's greedy heuristic                              | 33 |

| 2.10 | Puaut and Pais algorithm                                 | 33 |

| 2.11 | Specialised instruction example                          | 39 |

| 2.12 | A simple hotspot                                         | 40 |

| 2.13 | A sparse matrix multiplication.                          | 43 |

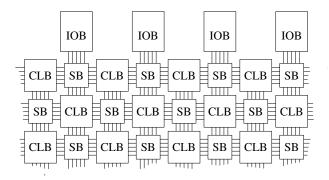

| 2.14 | An island-style FPGA                                     | 47 |

| 2.15 | A shift register, used to configure some FPGA components | 47 |

| 2.16 | Example of ASIP code                                     | 51 |

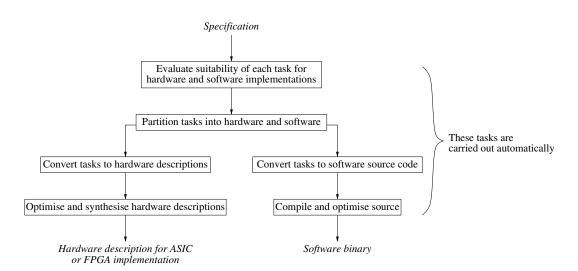

| 2.17 | The idealised co-design process.                         | 52 |

| 2.18 | Molen source code annotations                            | 54 |

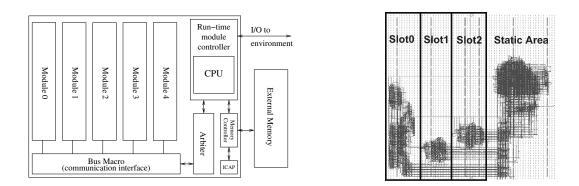

| 2.19 | Pictures of Karlsrühe project architecture               | 54 |

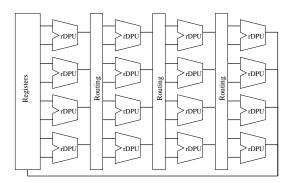

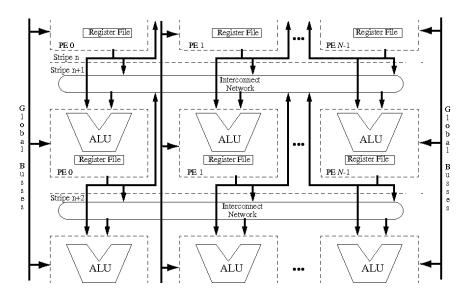

| 2.20 | Simplified CGRA                                          | 56 |

| 2.21 | KressArray example                                       | 58 |

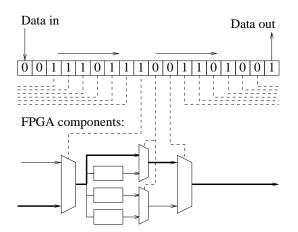

| 2.22 | Binary data, embedded in C source                        | 59 |

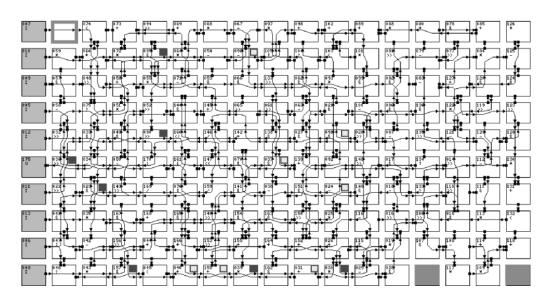

| 2.23 | The Rapid CGRA interconnect                              | 59 |

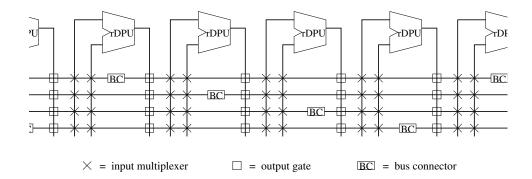

| 2.24 | Diagram of Piperench CGRA                                | 60 |

| 2.25 | The Garp architecture                                    | 61 |

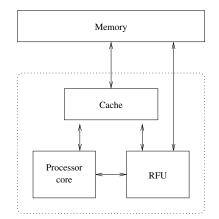

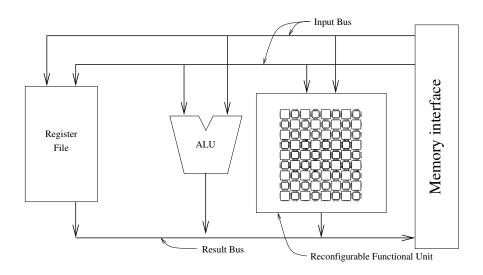

| 2.26 | Idealised RFU architecture                               | 62 |

| 2.27 | The Chimaera Architecture                                | 63 |

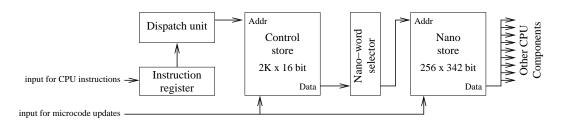

|      | Two-level indirection in QM-1                            | 66 |

| 2.29 | An architecture represented as a multi-level structure   | 69 |

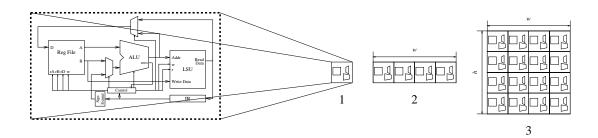

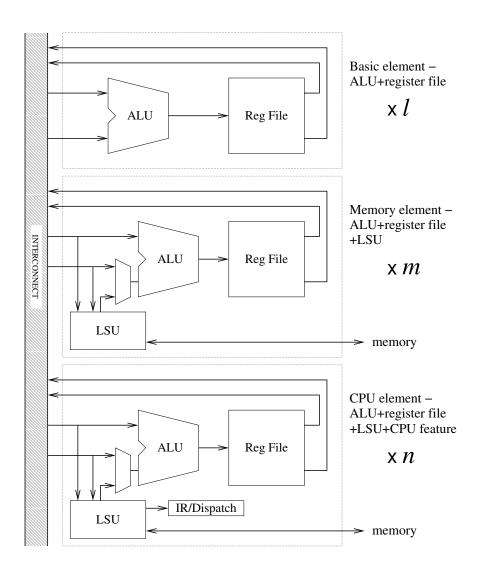

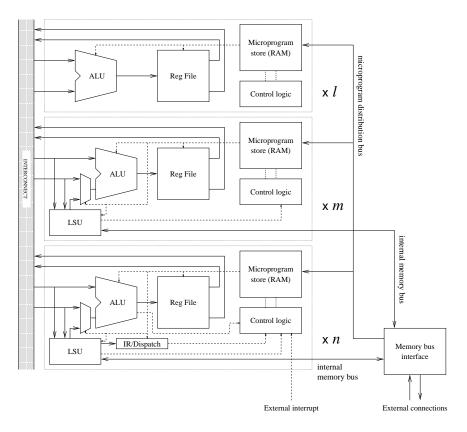

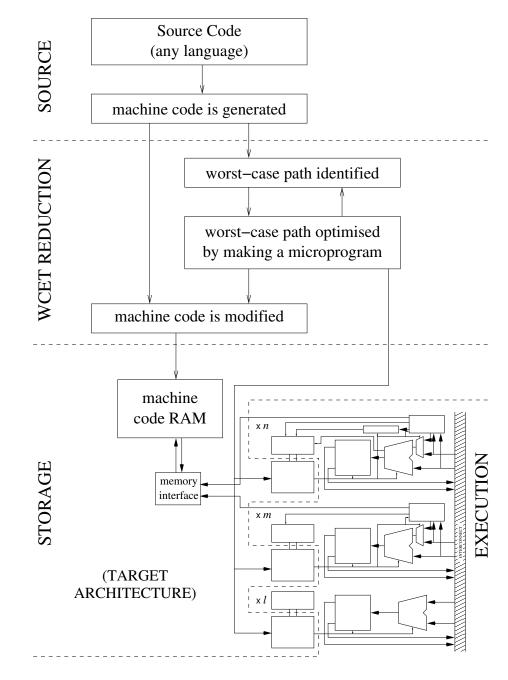

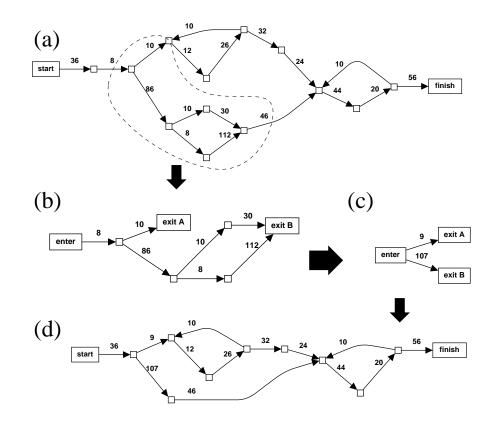

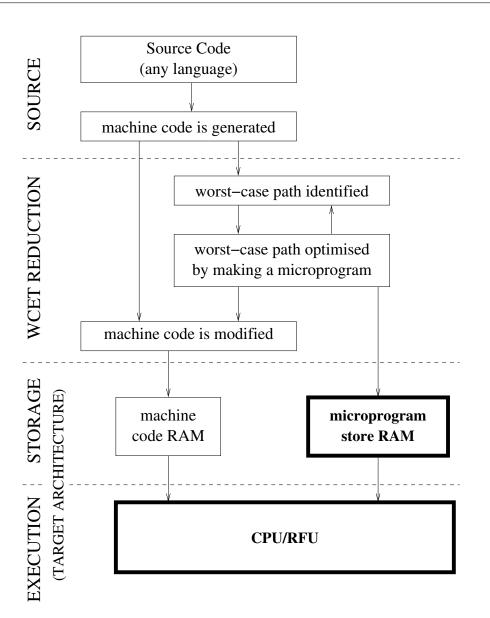

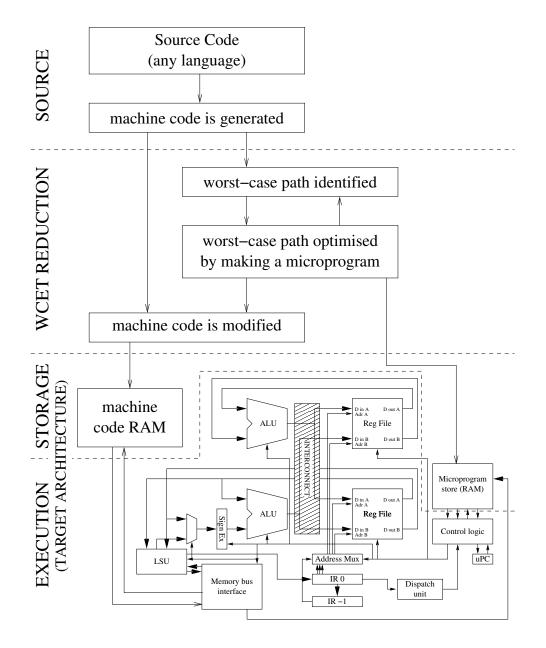

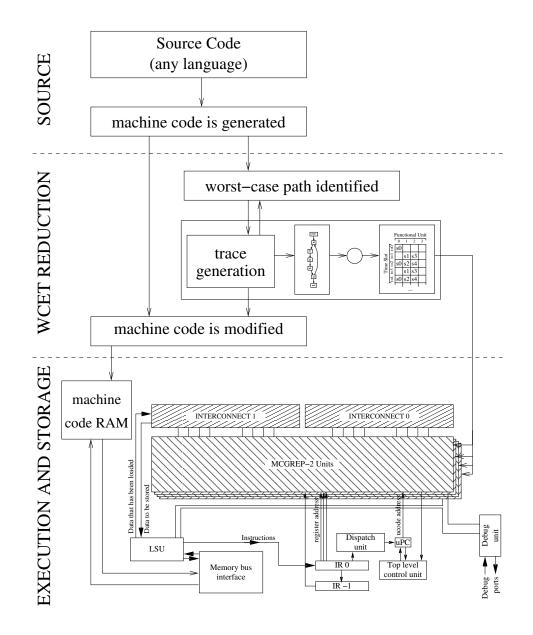

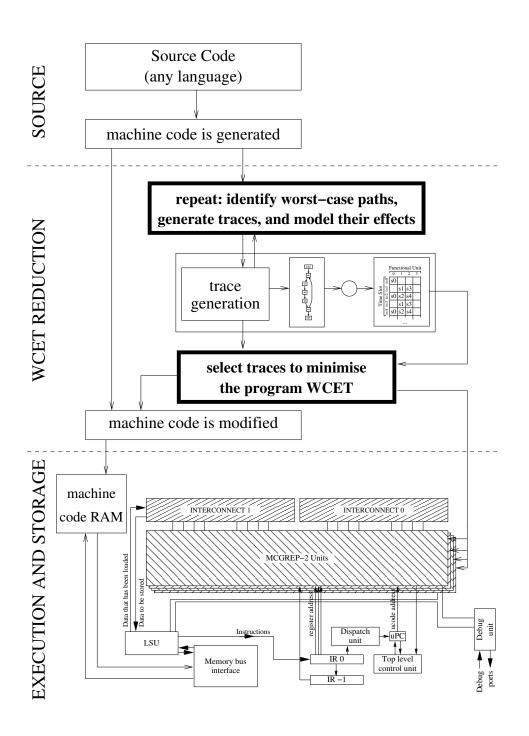

| 4.1  | WCET Reduction Process                                   | 80 |

| 4.2  | Simple CPU data path                                     | 82 |

| 4.3  | Contrasting array shapes                                 | 84 |

| 4.4  | Abstract high-level view of architecture                 | 86 |

| 4.5  | High-level view of architecture with microprogram stores | 88 |

| 4.6  | WCET Reduction Process plus CPU and RFU                  | 89 |

|      |                                                          |    |

| 4.7  | Transformation applied to execution path graph             | 91 |

|------|------------------------------------------------------------|----|

| 5.1  | WCET Reduction Process: CPU/RFU Implementation             | 96 |

| 5.2  | Components required                                        | 97 |

| 5.3  | Tradeoffs in simulator design                              | 98 |

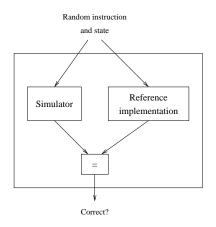

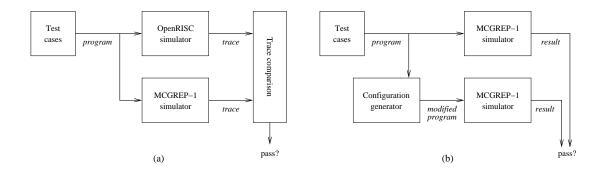

| 5.4  | Verification of a simulator                                | 99 |

| 5.5  | Sample usage of microcode container                        | 01 |

| 5.6  | Part of the OpenRISC ISA implementation                    | 04 |

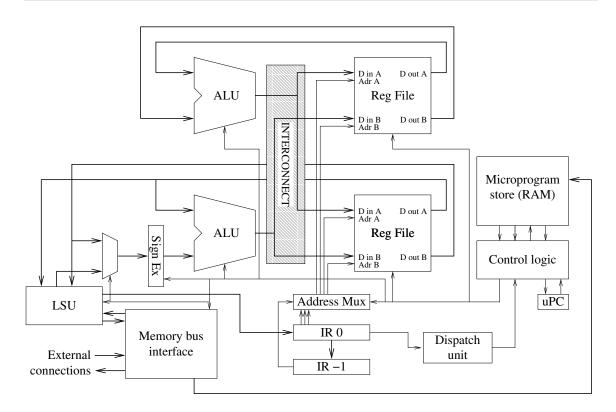

| 5.7  | Architecture diagram                                       | 06 |

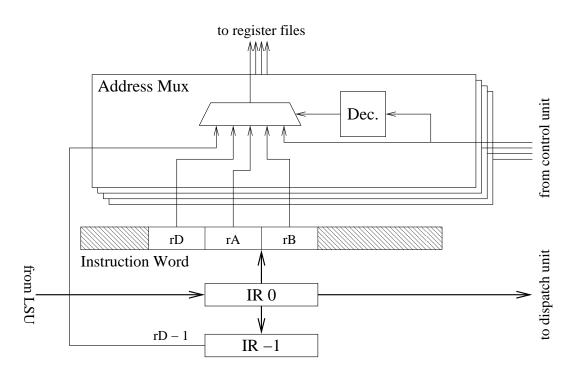

| 5.8  | Address mux: detail                                        | 08 |

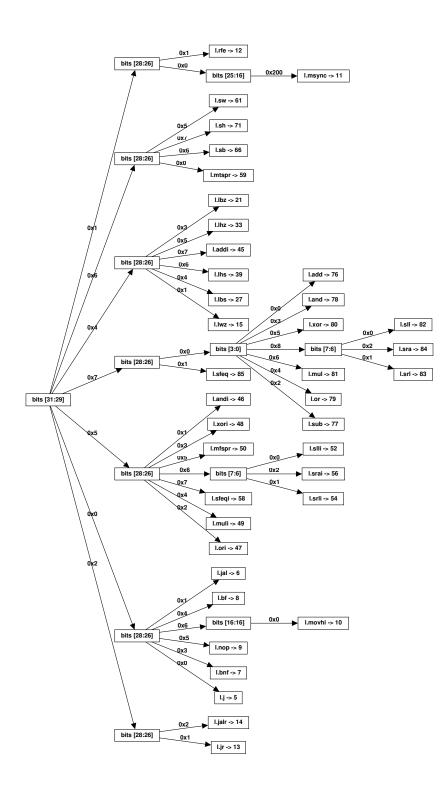

| 5.9  | Decoding tree for ORBIS32                                  | 10 |

| 5.10 | Branch to microprogram instruction                         | 11 |

| 5.11 | Diagram of microcode generator                             | 12 |

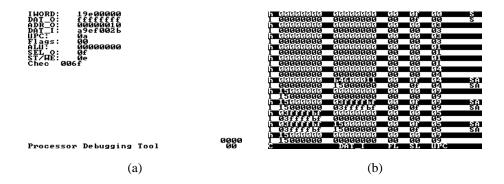

| 5.12 | GUI for micro-operation scheduling                         | 13 |

| 5.13 | WCET Reduction Process with MCGREP -1 1                    | 15 |

| 5.14 | Test diagram                                               | 17 |

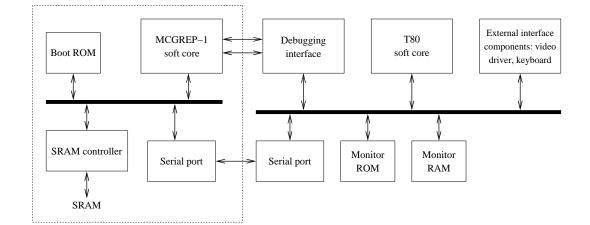

| 5.15 | Debugging monitor architecture                             | 18 |

| 5.16 | Integrated debugging monitor                               | 18 |

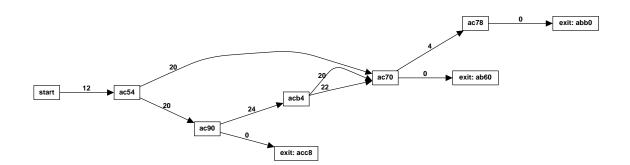

| 5.17 | Basic blocks in the sample WC path fragment (machine code) | 20 |

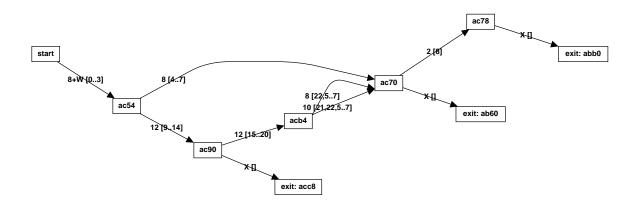

| 5.18 | Microprogram sequence for WC path fragment                 | 21 |

| 5.19 | Basic blocks in the sample WC path fragment (microprogram) | 22 |

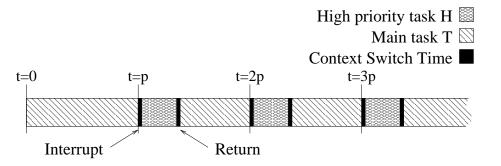

| 5.20 | Inter-task Interference Scenario                           | 22 |

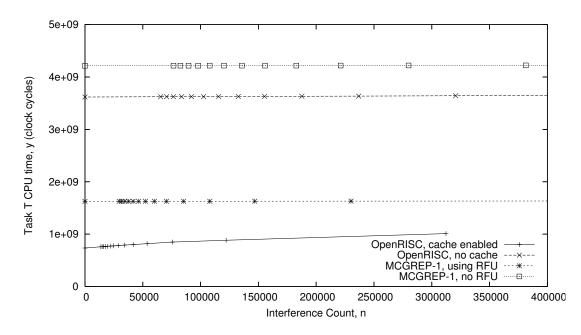

| 5.21 | Results of interference experiment                         | 24 |

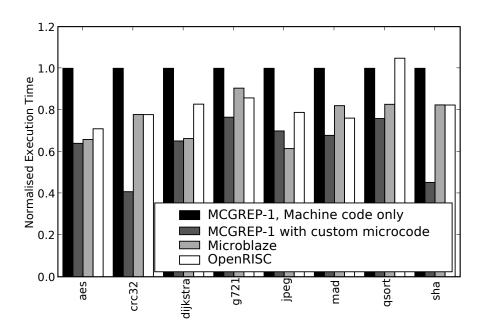

| 5.22 | Benchmark execution times                                  | 28 |

| 6.1  | WCET Reduction Process: Extensible CPU/RFU Implementation  | 34 |

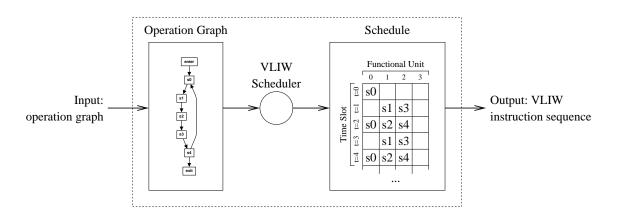

| 6.2  | VLIW scheduler overview                                    |    |

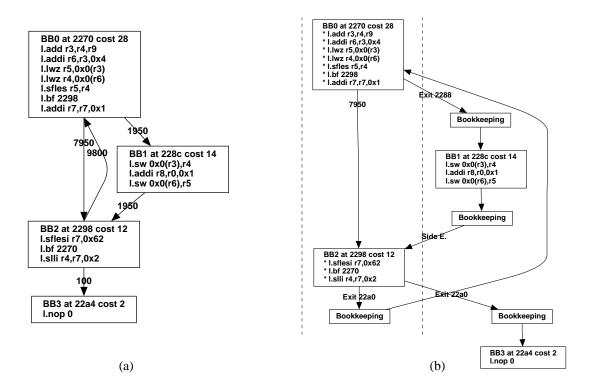

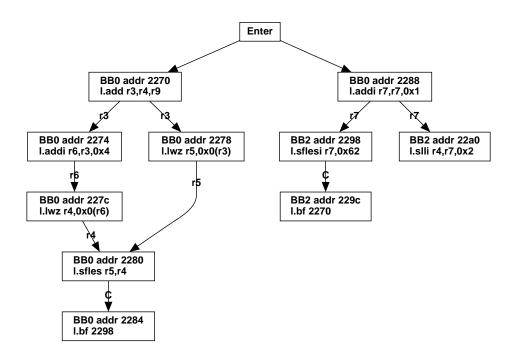

| 6.3  | Trace Scheduling Example                                   | 37 |

| 6.4  | Data Flow Graph                                            | 38 |

| 6.5  | Compaction Process                                         | 39 |

| 6.6  | Tail Duplication Example   1                               | 41 |

| 6.7  |                                                            | 47 |

| 6.8  | Microexecution Trace                                       | 48 |

| 6.9  | System Microprogram                                        | 49 |

| 6.10 |                                                            | 51 |

| 6.11 |                                                            | 55 |

| 6.12 | Microprogramming Example                                   | 57 |

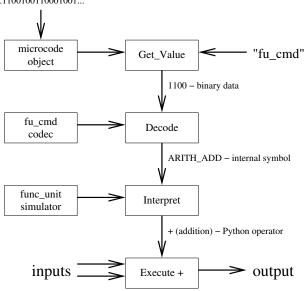

| 6.13 | Simulator decoding steps                                   | 58 |

| 6.14 | Architecture of MCGREP-2 simulator                         | 60 |

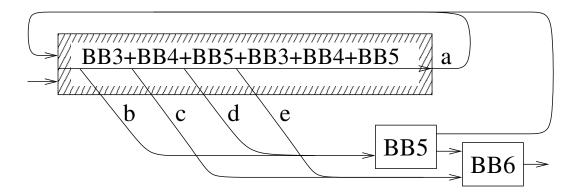

| 6.15 | Structure of a trace                                       | 64 |

| 6.16 | WCET Reduction Process: MCGREP-2 Implementation            | 71 |

| 6.17 | Checkpoint and hotspot marker instructions                 | 74 |

| 6.18 | Marker added to C code                                     | 76 |

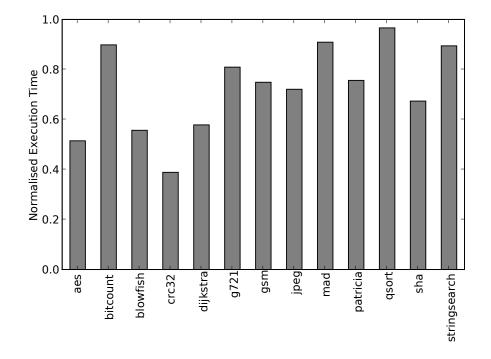

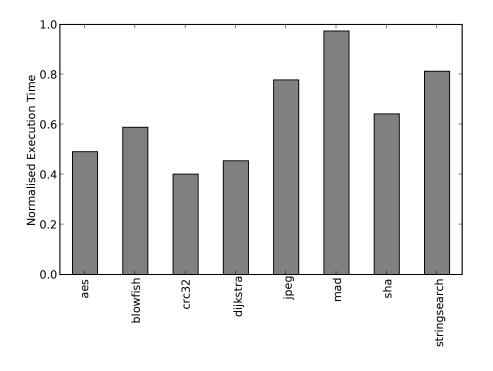

| 6.19 | Benchmark execution times                                  | 83 |

| 6.20 | Multiple contexts example                                  | 86 |

|      |                                                            |    |

| 6.21        | Multiple context timings                                                        |

|-------------|---------------------------------------------------------------------------------|

| 6.22        | Effects of changing array size                                                  |

| 6.23        | Effects of increasing trace length                                              |

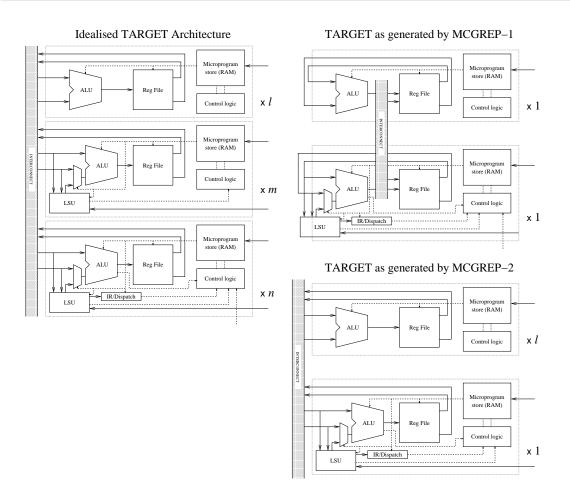

| 6.24        | Implementations of TARGET                                                       |

| 7.1         | WCET Reduction Process: Missing Components                                      |

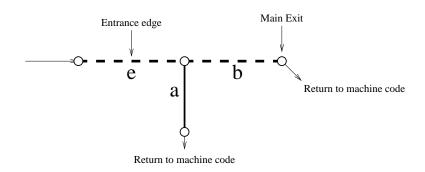

| 7.2         | A trace as part of a T-graph                                                    |

| 7.3         | Score heuristic                                                                 |

| 7.4         | WC path finding heuristic                                                       |

| 7.5         | The <i>Find_Candidates</i> procedure finds and evaluates candidate traces       |

| 7.6         | Framework for E.T. measurements                                                 |

| 7.7         | Bubble sort C source                                                            |

| 7.8         | Developer-specified constraints for Figure 7.7                                  |

| 7.9         | "EPET" Results, 1                                                               |

| 7.10        | Length and Microprogram Store Space                                             |

| 7.11        | Effects of changing $W$                                                         |

| 7.12        | Basic block graph of bubble (Figure 7.7)                                        |

| 7.13        | Effects of changing W: improved heuristic                                       |

| 7.14        | Hybrid Architecture                                                             |

| 7.15        | WCET Reduction Process: Scratchpads                                             |

| 8.1         | Results for section 8.3                                                         |

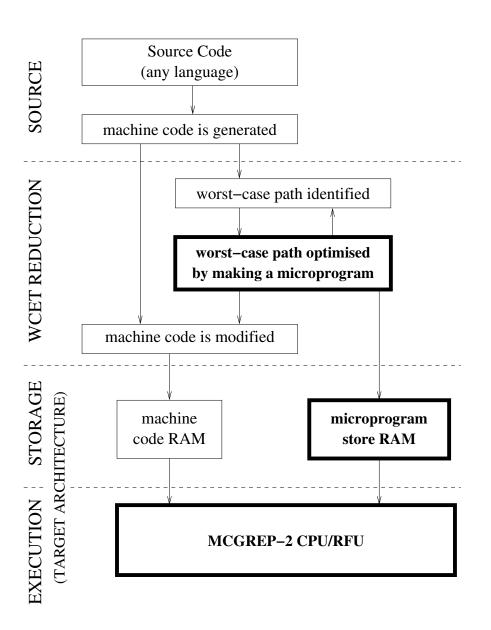

| 8.2         | Final WCET Reduction Process                                                    |

| 8.3         | Improvements with different architectures                                       |

| 0.5         |                                                                                 |

| A.1         | Software Map                                                                    |

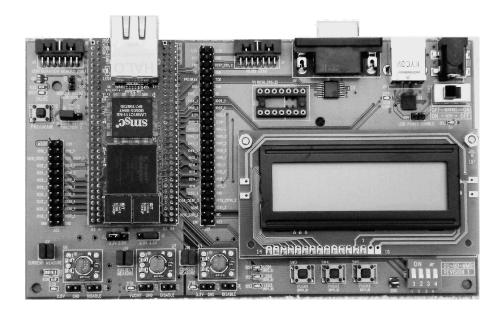

| A.2         | MM1 Photograph                                                                  |

| <b>B</b> .1 | Hotspot Example                                                                 |

| B.1<br>B.2  | Bubble sort inner loop, as ORBIS32 assembly. C source appears in Figure 7.7 293 |

| <b>D</b> .2 | bubble soft miler loop, as OKD1352 assembly. C source appears in Figure 7.7 23  |

| D.1         | Benchmark execution times                                                       |

| E.1         | Sample T-graph                                                                  |

| E.2         | GLPK Commands for Example                                                       |

| 1.2         |                                                                                 |

| F.1         | Example Trace                                                                   |

| G.1         | Extended <i>Find_Candidates</i>                                                 |

| G.2         | Percentage WCET reduction for each case                                         |

|             | -                                                                               |

For Jillian

# Acknowledgements

This work would not have been possible without the advice of my supervisor, Dr Neil Audsley, who has read many drafts of this work and earlier publications. I would also like to thank current and former staff and students of the Real-Time Systems Group at the University of York for their support. Special thanks to Adam Betts for his advice regarding WCET analysis issues, to Andrew Borg, Rui Gao, Ian Gray, Nick Lay and Ameet Patil for their help in the lab, and to Michael Ward and Andy Wellings for their advice on publications. Thanks also go to my examiners, Iain Bate and Mark Zwolinski, who made many suggestions for improvements to this work.

I must also thank the authors of all the work cited in chapter 10, and the authors of the freely redistributable software and IP used by my experiments (appendix A), including Python [208], gcc [94], and the OpenRISC CPU core [150]. This work would have been significantly more difficult without access to free software and hardware designs.

Finally, I would like to thank my family and friends for putting up with me as I completed this work. In particular I would like to thank my fiancée Jillian, my parents Susan and Peter, and my friends from UoY.

# Declaration

This thesis has not previously been accepted in substance for any degree and is not being concurrently submitted in candidature for any degree other than Doctor of Philosophy of the University of York. This thesis is the result of my own investigations, except where otherwise stated. Other sources are acknowledged by explicit references.

Some parts of the thesis are also described by existing publications. The MCGREP-1 implementation and experiments (chapter 5) are summarised by [276]. The MCGREP-2 simulator (section 6.2.5) is described by [277]. The IPET-based WCET reduction algorithm and experiments (chapter 7) and the evaluation against instruction scratchpads (chapter 8) are described by [278]. All of these publications were written by myself with advice from my supervisor, Dr Neil Audsley.

I hereby give consent for my thesis to be made available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.

## **Chapter 1**

# Introduction

Almost every modern home and workplace contains many computers. Some of these computers are immediately recognisable as laptops and desktop PCs, but many are hidden within *intelligent devices* that use software to implement functionality. These computers are *embedded systems*. They have been widely used in place of discrete electronics within televisions, radios, video cassette recorders and washing machines for more than two decades. A common definition of the term is as follows ([25], "Embedded System"):

"A combination of computer hardware and software, and perhaps additional mechanical or other parts, designed to perform a dedicated function. In some cases, embedded systems are part of a larger system or product, as in the case of an anti-lock braking system in a car."

Intuitively, including a computer within some devices might seem like overkill. Does a toaster *really* need a microchip? Clearly not - toasters predate microelectronics, as do televisions, radios and video recorders. But the embedded system is an answer to a problem: *how can the manufacturing cost be minimised*?

Perhaps surprisingly, using an embedded system actually *reduces* the cost of developing and building a television. The reason is a property of manufacturing - *economy of scale*. If every embedded system was composed of custom-made "application specific" components, such as a clockwork timer that could only fit within a specific model of toaster, the design and build costs would be very high. Each component would have to be designed for the new model.

While each embedded system has a dedicated function, very few parts of a typical embedded system are truly application specific. Some components such as *central processing units* (CPUs) [123] and memory are found in all embedded systems. Many other components can be found in all embedded systems of a particular class: for example, MPEG-2 video decoders may be found in both DVD players and digital satellite receivers.

Each of these components must be customisable for a range of applications. A CD player and a washing machine may include the same type of CPU, but the functions required are very different. Therefore, a different *configuration* is applied by the embedded system manufacturer, most commonly in the form of a *program*. A program is *software*: it specifies the actions to be carried out by a processor. This flexibility allows one device to be reused for many different applications. A generic component can be mass produced, then bought "off the shelf" and configured for use in an embedded system with any purpose: a CD player, washing machine, or television. All that is required is the appropriate software.

Software effectively creates the *functionality* of an embedded system. It is possible to translate a program into hardware, but this does not scale to a program of any size because of the need to place and route interconnections between program components [271]. On the other hand, software does scale well: the limit on a program's size is generally only imposed by the size of the computer's memory.

But software has a disadvantage. It is *sequential*, meaning that operations always take place in a defined order. This raises a second problem: *how can the speed of software operations be optimised*?

Many clever techniques have been applied to solve this problem [228, 144, 85, 236, 211, 101, 168, 103, 240, 139], with a great deal of success in reducing the *average* execution time of a program. CPUs for embedded systems can make use of some of these techniques to run programs faster.

However, this extra speed comes with a cost. When certain CPU features are enabled [167, 121, 275], it is difficult to calculate the longest time required to run a program (or part of a program). This is important when the program has to interact with external components: the program may have to respond in *real-time* to an event from elsewhere, perhaps turning off a washing machine water heater before the temperature gets too high, or ejecting some toast before it burns.

In general, this problem is expressed in terms of *deadlines*. A program with deadlines that must be met is said to be *real-time*, because it must respond to real world events in a timely fashion [43]. Such requirements introduce many issues, touching virtually all aspects of system design. Thus, the system is known as a *real-time system* (RTS), and is further described as *hard real-time* if deadlines are strict.

Because some CPU features can make program timing analysis difficult, it is not always easy to be sure whether a program running on certain types of CPU can *safely* be used as part of a larger embedded system. A hard real-time system can only be described as safe if deadlines are always met. So there is a third problem: *how can speed be increased while preserving safety?*

Methods exist to determine whether a program will meet its deadline when running in a particular environment [205]. These operate by computing the *worst case execution time* (WCET) of the program: the longest period of time that could possibly be required to run the program, in the worst possible input conditions. Sophisticated methods exist to perform this *timing analysis* [192, 159, 207, 34, 280], but it is not always easy to apply these to a particular CPU or program. Simply put, CPUs are very complex, and this makes them difficult to model.

A variety of solutions have been proposed for this problem, including CPUs that facilitate timing analysis [9, 69, 217], application specific hardware [20, 215], new execution paradigms [204, 61], and using reconfigurable hardware [260]. All of these solutions are interesting, and all are focused on a single problem: *what is the best way to build an architecture to make timing analysis easy?*

In this work, it is assumed that an embedded system is used to implement some group of software tasks that have hard deadlines. Given this assumption, the work examines possible answers to the problems identified above, specifically:

- How can the speed of real-time software operations be optimised?

- How can speed be increased while preserving safety?

- What is the best way to build an architecture to make timing analysis easy?

This is done by looking at the properties of architectures that could provide answers to these problems, and at the requirements and capabilities of WCET analysis tools. This information is used to propose, specify, implement and test a new architecture for embedded hard real-time systems. This architecture is then applied to the problem of increasing execution speed in a predictable fashion.

### 1.1 Thesis Aims

This work aims firstly to explore the architectural issues relating to the problems outlined above. Next, a new CPU architecture for embedded hard real-time systems will be characterised, prototyped and implemented. Finally, this architecture will be evaluated as a possible solution to the problems.

The new CPU architecture will be part of the recent trend towards architectures that facilitate timing analysis [69, 9, 204, 217] for hard real-time systems. It will extend existing work to move closer to the ultimate goal of that trend: a scalable CPU architecture that enables program WCETs to be (a) estimated accurately, and (b) reduced. To do that, the following subgoals must be satisfied by the new CPU architecture:

#### • Amenability to timing analysis.

The CPU architecture will be designed to support the best methods of timing analysis found in previous work. It will only be possible to consider an architectural feature if it supports such analysis.

### • Reduction of worst case execution time.

Simple CPU architectures support timing analysis very well, but lack the performance required to support some real-time applications. Conventional approaches only improve average performance. This might not improve the worst case performance at all, and it might make the worst case performance more difficult to quantify. So a different approach is needed for hard real-time systems design, as an architectural feature has only provided an improvement if the WCET is reduced as a result of its presence.

#### • Structural scalability.

Structural scalability is a property defined [39] as:

"a system...[is]...structurally scalable if its implementation or standards do not impede the growth of the number of objects it encompasses, or at least will not do so within a chosen time frame."

Some platforms for hard real-time systems do not meet this requirement. For example, the space available for "hardware threads" in [1] is limited by physical hardware space. And while [129] can support an unlimited number of different co-processors through run-time reconfiguration of hardware, the co-processors are non-relocatable and strictly limited in size. The new CPU architecture must avoid putting restrictions on the number of tasks or the size of tasks to avoid being limited to systems of a certain complexity.

## **1.2 Digital Appendix**

This work comes with a companion data archive, containing software, hardware designs and experiments written to support the work. Documentation for the archive is provided in Appendix A, but references to specific programs and files can also be found throughout this document. These references take the form shown below:

### Some of the files in the archive

> /README.txt

Documentation file, in the root directory of the archive.

> /install.sh

Installation program.

> /mcgrep1

Support files for chapter 5.

### 1.3 Thesis Structure

The layout of the thesis is as follows. This chapter sets out the objectives. Chapter 2 looks at related work, then chapter 3 describes the motivation and hypothesis for the work. Chapter 4 sets out a proposed architecture as an answer to the problems listed here, which are followed in chapters 5 and 6 by two architecture implementations: first a static prototype, then an extensible refinement. Chapter 7 describes a WCET reduction algorithm that makes use of the proposed architecture, and chapter 8 evaluates it against previous work. Finally, chapter 9 concludes the work with a summary of the findings.

## Chapter 2

# Literature

This work aims to characterise and implement a CPU architecture for embedded hard real-time systems, meeting the requirements defined in section 1.1. This literature review is divided into two major parts:

In sections 2.1 to 2.3, research in the field of worst case execution time analysis is reviewed. The problems caused by complex CPU architectures are examined, and previous solutions are described. The aim of this part is to provide an understanding of issues related to the requirement for amenability to timing analysis.

In sections 2.4 to 2.6, various methods that could be used to improve the worst case performance of embedded systems are reviewed. The aim of this part is to provide an understanding of the performance improvement methods that may be used when reducing worst case execution time is the issue, and amenability to timing analysis and scalability are also requirements.

### 2.1 About Timing Analysis

In section 1.1, the requirements state that the CPU architecture must be amenable to timing analysis.

Timing analysis is an essential part of guaranteeing the *schedulability* of a hard real-time system. Consider a hard real-time system as a program composed of one or more *tasks*. Given this commonly-used model, schedulability analysis is [214]:

"...the process of deciding whether or not a scheduler can schedule a particular set of tasks without missing any deadlines."

Schedulability analysis is carried out using information about the CPU time required by each task. Because it is important to guarantee that deadlines are met in the worst possible case, the worst possible time requirement is used for each task. This time is known as the *worst case execution time* (WCET), and it is determined by analysis for a particular task and a particular CPU architecture. According to Puschner and Burns [205]:

"WCET analysis computes upper bounds for the execution times of pieces of code for a given application, where the execution time of a piece of code is defined as the time it takes the processor to execute that piece of code."

In the general case, exact schedulability analysis is intractable [46]. However, it is possible for specific cases, such as models that involve only *periodic tasks* [141] (which execute with an exact frequency), and models that use server tasks to isolate aperiodic activities [43]. Schedulability

analysis is a part of software design, and it is therefore outside of the scope of this work. However, the requirements of schedulability analysis are important in the sense that they partly define the properties of effective WCET analysis tools.

WCET estimates are often used because computing an exact WCET value for a general program is difficult for reasons that are discussed in the following sections. However, estimates can be very close to the actual WCET value. Estimates are required to be [205]:

- Safe: greater than or equal to the actual worst execution time for the task,

- **Tight**: as close as possible to the actual worst execution time for the task.

The first requirement ensures that schedulability analysis will always provide each hard real-time task with sufficient time to complete its work before its deadline. The second requirement aims to minimise this time allocation, so that the CPU resources can be used efficiently by other tasks.

WCET estimates are dependent on both the application and the hardware it runs on, including the CPU and memory system, because all hardware components can affect execution time. WCET analysis tools conventionally assume that the application will not be interrupted by other applications or operating system routines [205], because the timing effects of such *interference* are unbounded.

#### 2.1.1 WCET Estimation

A naïve approach for WCET analysis would involve simple execution with different data sets. However, in the general case, it is not possible to tell if a measured execution time really represents the worst case. Nor is it possible to evaluate the time for *all* possible input data by running the program with each possible input (an "*explicit path enumeration*" approach), because that would require at least  $O(2^n)$  operations for *n* bits of input.

However, it is possible to directly compute the WCET of small sections of a program. At the lowest level, programs are composed of *machine instructions*: primitive operations that are interpreted by a CPU. In any sufficiently simple CPU, the execution time of each instruction is either a fixed quantity (e.g. 1 clock cycle), or dependent on some external constant such as the latency of the memory. WCET analysis is simple at this level because the instruction execution time is not dependent on inputs. The problem remains simple for any block of code that is not dependent on either execution history or external input. One example of part of a program with these properties is called a *basic block*: a sequence of instructions containing exactly one branch instruction, located at the end.

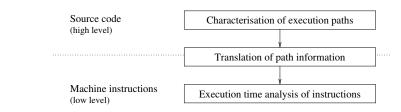

WCET analysis combines low level measurements of block execution times with high level path information. The analysis problem spans three domains as shown in Figure 2.1: source code (which provides the path information), machine instructions (which are used to calculate execution times), and a translation step to move information between the preceding two.

The WCET value is often an estimate rather than an exact value because automatically enumerating all possible paths through the program is not possible in general [205]. For example, calculating the number of iterations needed to complete a loop is undecidable [159] (this is the *halting problem*). This is why the high level source code must be consulted for information about execution paths. WCET analysis tools rely on the user to explicitly indicate path information, such as the maximum number of iterations of a loop. This is often done using annotations embedded in source code [206, 50] or separate source files [192]: effectively, the annotations are constraints

Figure 2.1: The three problem domains for worst case execution time analysis.

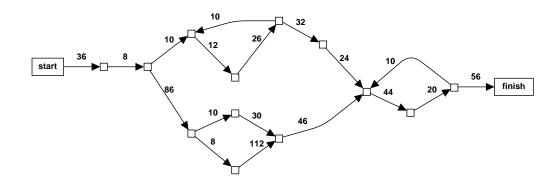

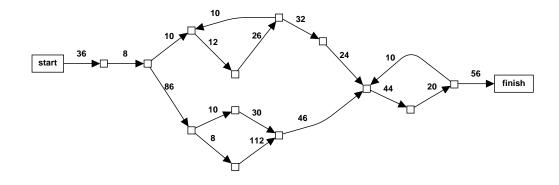

**Figure 2.2:** An execution path graph for a simple program, based on an example from [207]. The graph edges represent basic blocks, and each is labelled with the time cost of executing it. The units could be any measurement of time: CPU clock cycles is common. Nodes represent branch points, where execution flow may take one of two or more directions, and join points, where multiple flows lead to the same block. The program contains two loops: the maximum number of iterations of each of these will need to be bounded by some sort of constraint.

on program behaviour. A safe WCET estimate for a program may be produced by the following basic process [205]:

- Compilation of the program [2] to obtain machine instructions from source code.

- Characterisation of execution paths generate a graph of execution paths through the program, based on high level language semantics, annotations, and other constraints. A sample graph for a simple program is shown in Figure 2.2.

- Translation of path information obtain the machine code for each edge of the graph.

- Execution time analysis the WCET of each edge is computed using the machine code. Each edge is labelled with its WCET.

- Recursively collapse the graph using simple rules that preserve safety [28]. These rules merge subgraphs into single edges, with a new WCET:

- 1. The WCET of a sequence of edges is the sum of the WCETs of each individual edge.

- 2. The WCET of a conditional branch (e.g. *if*) is the WCET of the most expensive branch direction, plus the overhead for evaluating the condition.

- Figure 2.3: This example illustrates two infeasible paths. If statement (1) is executed, statement (4) cannot be executed. Similarly, if statement (2) is executed, statement (3) cannot be executed.

- 3. The WCET of a loop is the maximum WCET of the loop contents, multiplied by the maximum number of iterations, according to the source code.

The result of this process is a graph with one node, labelled with the WCET estimate for the entire program.

This simple WCET analysis method will produce a value that is guaranteed to be safe, provided that the edge WCETs have been computed correctly, but there is no guarantee of tightness. The WCET estimate may be very pessimistic, i.e. much larger than the actual WCET. This is because it is not possible to incorporate all of the constraints that affect execution into the analysis, so more elaborate methods are usually required.

#### 2.1.2 Reducing Pessimism in WCET analysis

WCET estimates need to be as close as possible to the actual WCET so that CPU resources can be allocated efficiently. The problem of reducing the overall pessimism of the WCET analysis process is the subject of ongoing research.

One source of pessimism is inadequate modelling of execution path constraints. Bounding loops and recursion makes safe WCET estimation possible, but it does not provide information about *infeasible paths*. A simple example is provided in Figure 2.3. Given this example, a simplistic WCET analyser will examine each if statement in isolation. This produces a safe but pessimistic WCET estimate of max(55, 10) + max(5, 50) = 55 + 50 = 105, using the execution times of blocks (1) and (4). However, no path through (1) passes through (4): the only possible paths are [(1), (3)] and [(2), (4)]. The actual WCET is max(55 + 5, 10 + 50) = 60.

This can be avoided to some extent by analysis of high level source code: Altenbernd [4] describes symbolic execution of source code to store information about constraints that are known to hold along possible execution paths. For example, the constraints set by block (1) in Figure 2.3 eliminate block (4) from consideration.

Generally, symbolic execution is called *abstract interpretation* (AI). The benefits of AI go beyond detecting infeasible paths: AI can also be used to derive other execution constraints in some

| Constraint                       | Effect                                                    |

|----------------------------------|-----------------------------------------------------------|

| loop L [1,10] times;             | Loop L repeats at least once and at most 10 times.        |

| samepath(A,C);                   | When statement A executes, statement C always executes,   |

|                                  | and vice versa.                                           |

| (not A) imply loop L 10 times;   | If A is not executed, loop L is repeats exactly 10 times. |

| execute A [0, 1] times inside L; | During execution of L, statement A will execute at most   |

|                                  | once.                                                     |

Table 2.1: Examples of IDL statements from [192].

```

procedure A ( N : POSITIVE ) is

begin

--{ loopcount (1,N);

for I in POSITIVE range 1..N loop

--# assert TRUE;

--{ loopcount (I,N);

for J in POSITIVE range I..N loop

--# assert TRUE;

S;

end loop;

end loop;

end A;

```

**Figure 2.4:** Annotations in a procedure indicate the bound on the total number of loop iterations, from [49] page 101. These allow a WCET analysis tool to calculate that statement s will only execute  $\frac{1}{2}n(n-1)$  times, rather than  $n^2$  times which would be assumed if the bounds on both loops were fixed. Two types of annotation are seen here: conventional SPARK/Ada annotations (--#) and timing annotations (--{) as proposed in [50].

cases, including loop bounds. In [78], Ermedahl and Gustafsson describe a method for finding all constraints within programs written in a subset of C or Smalltalk. Their approach runs the program but considers all variables as a feasible range of values rather than a single value. This can be used to discover some loop bounds and infeasible paths automatically, independently of the input.

However, these approaches will not work in all cases since deriving constraints is equivalent to the halting problem in general. Therefore, ways to specify information about loops and infeasible paths are always needed. In [192], Park describes the use of a constraint language ("IDL") with powerful features for expressing the relationships between statements. Some examples are illustrated in Table 2.1. These constraints are placed in a separate source file and linked to program source files via labels attached to statements. Using this model, constraints can be easily applied to any subset of all statements, regardless of their scope or encompassing function.

An alternate (but essentially equivalent) approach is to place these annotations directly in source code. In [50], Chapman et al. describe extensions to the SPARK/Ada language for hard real-time systems. At the time, SPARK already included an annotation mechanism which was used to prove program correctness [49]. Chapman extended this mechanism to support new timing annotations that are similar to the existing SPARK syntax. A sample annotated procedure is shown in Figure 2.4.

Through path constraints of this type, it is possible to express all possible program behaviour,

| Variable    | Meaning                                                                         |

|-------------|---------------------------------------------------------------------------------|

| f(x)        | Upper bound on number of executions of basic block $x$ , given all constraints. |

|             | Computed by integer linear programming algorithm.                               |

| $\gamma(x)$ | Execution time of basic block x. Constant.                                      |

| $Z_G$       | Program WCET, defined by equation 2.1.                                          |

**Table 2.2:** Variables specified by the integer linear programming model of Puschner and Schedl [207]. The integer linear program selects the values of f(x) that maximise  $Z_G$ .

not just infeasible paths. The *implicit path enumeration technique* (IPET) approach to WCET analysis proposed by Li and Malik [159] applies these constraints to an execution graph by expressing them as inequalities. For example, if a statement n is executed f(n) times, then the constraint that statement A executes once for every five executions of B is expressed as 5f(A) = f(B).

For IPET, the WCET  $Z_G$  of an execution path graph G = (V, E) is defined by this equation:

$$Z_G = \sum_{x \in E} \gamma(x) f(x) \tag{2.1}$$

where  $\gamma(x)$  is the time cost of executing a basic block x, and f(x) is the number of times that basic block will be executed in the worst case. Each  $\gamma(x)$  is computed using a CPU model and has a constant positive integer value. Each f(x) is computed by using an *integer linear program* to calculate the values of f(x) that maximise  $Z_G$ . This is possible because the value of f(x) for a basic block x is constrained by f for x's successors and predecessors, and by constraints specifying infeasible paths, loop bounds, and other execution bounds. Through IPET, the WCET analysis problem is mapped onto a form of constraint problem. An example of the IPET process is given in Appendix E.

Puschner and Schedl [207] have shown that the exact WCET value for a program can be computed if the complete set of path constraints for the program are specified. (A second implicit assumption is that  $\gamma(x)$  is constant for each basic block x.) The proof is based on a formal model using the same approach as Li and Malik. In this model, the total number of executions of each piece of code is expressed as a parameter of the circulation problem from graph theory [63]. The program is expressed as a *timing graph* (T-graph) in which every edge x is a piece of non-branching code, labelled with a known (constant) execution time ( $\gamma(x)$ ) and a "flow value" (f(x)) that represents the upper bound on the number of executions of the associated code. Nodes represent branches and join points, and each has the property that  $\sum f$  for all incoming edges is equal to  $\sum f$  for all outgoing branches. Table 2.2 lists the variables involved. Additional bounds on f are applied using path constraints like the ones listed in Table 2.1.

The model is then transformed to a series of inequalities that describe the graph structure and all the constraints that apply to it. Like the inequalities used in the Li and Malik model, these are solved as an integer linear programming problem, which computes worst case values for the number of executions of each edge (i.e. f) such that  $Z_G$  is maximised.

Integer linear programming is an elegant way to combine structural information about a program with path constraints. It allows infeasible paths to be eliminated, handles bounds on loops and recursion, and is capable of supporting complex constraints such as non-rectangular loops (e.g. where an outer loop executes once for each x from 1 to 100, and an inner loop executes once for

each y from 1 to x). Path constraints can even be used in the manner of procedure parameters to propagate constraint information from callers to callees - a symbolic annotation approach for this purpose is proposed by Bernat and Burns [33].

A potential disadvantage of the approach is that the integer linear programming problem is NPhard. Algorithms to solve it require  $O(2^n)$  steps in general. (The topic of algorithmic complexity is revisited in section 2.4.1.) However, Li [159] observed that when the path constraints are restricted to those available in IDL (e.g. those in Table 2.1), "the integer linear programming problem is equivalent to a network flow problem, which can be solved in polynomial time."

#### 2.1.3 The Translation Step

Modelling the structure of a program is only one part of the task of WCET analysis. Low level information about the timing of each basic block of program code is also required. As Figure 2.1 illustrates, a translation step is needed to manage the relationship between high level execution path information and low level machine instructions.

Conventionally, machine instructions are produced from source code by a compiler [2]. Early compilers maintained a straightforward relationship between high level statements and machine code. With such a compiler, translating information between the high and low level domains is very simple, especially as the relationship between source code and machine code is already maintained for debugging purposes.

However, this type of machine code does not use CPU resources efficiently. To improve performance, compilers generally apply *optimisation* algorithms which preserve the *meaning* of code but change the low level structure so that CPU resources are used more effectively. (The effects of software optimisation are described in section 2.4.2.)

Optimisations make the translation step non-trivial [205] as structural information is partly lost. Two classes of translation approach have been demonstrated to handle this problem:

- Invasive approach: the compiler transforms execution path information at the same time as optimising code. This approach requires modifications to compiler source code, hence *invasive*. Compilers that have been extended with this feature include vpo (in [183]), gnat/gcc (in [169]), and lcc (in [162]).

- 2. **Co-transformation** approach: optimisations are applied outside the compiler by a second tool. This approach is demonstrated by Engblom [76], who proposes *optimisation description language* (ODL) as an input to a tool which applies optimisations and outputs information to match high level path information with low level machine instructions.

These approaches make it possible to carry out WCET analysis on optimised programs. This is essential for efficient use of a CPU.

### 2.1.4 CPU Modelling

The final problem domain of WCET analysis is the low level model used to calculate the execution time of pieces of code. High level WCET approaches have made the assumption that the execution time of each piece of code is constant, or at least outside the scope of discussion [207, 192, 159]. These assumptions hold for simple CPUs such as the Motorola 68000, where execution time is constant for each instruction [181], but are invalid for more modern CPUs where a number of features can cause the execution time of the same basic block to vary.

CPU design is a complex topic, but it is important to explain the nature of these features and the reasons for their introduction. This is an essential part of the work, because the requirements force an understanding of why state of the art CPUs are not amenable to timing analysis. If the state of the art is to be advanced, it is necessary to understand the ways in which current approaches are lacking. Therefore, discussion of WCET analysis is suspended at this point to make way for a digression into CPU technology. In section 2.3, the review of WCET analysis continues with an examination of the techniques that have been applied to account for modern CPU features.

### 2.2 A Brief History of CPU Technology

In the early days of computing, CPUs had to be built with minimal hardware. Electronics were bulky and expensive, there was no design automation, and components were unreliable [83]. The machine instructions understood by a CPU (the *instruction set architecture*, or ISA) had to be simple to keep construction and maintenance costs low. The invention of the *integrated circuit* (IC or *microchip*) enabled advanced CPUs to be mass-produced. The first complete CPU on a chip (*microprocessor*) was the Intel 4004 [137], built in 1971. Before this, CPUs had been built using multiple chips or discrete components, at a higher cost.

Since that time, economic forces have driven development of CPUs with higher performance. The performance (operations per unit of time) of a CPU may be measured in *millions of instructions per second* (MIPS), but the use of standardised benchmark programs [108, 154, 70] is often preferred because MIPS values are not comparable between CPU types and do not indicate the number of operations actually completed by each instruction. Benchmarks measure the time taken to accomplish a particular task, providing a metric for overall CPU performance that is independent of low level details such as the ISA.

Note that it is important to distinguish between architectural features that provide improved *average* performance and those that provide *guarantees* about improvement. Many performance improvement mechanisms are not well suited to providing guarantees about timing: they are very effective at improving performance, but only in the "most likely" cases. In other words, they reduce the *average case execution time* (ACET) of typical programs, but they do not make any guarantees about WCET. One characteristic of such CPUs is that the execution time of any particular basic block depends on what has been previously executed. CPUs with this history dependence property are said to lack *basic block timing invariance*.

In general, performance improvements are limited by engineering issues. Two such "bottlenecks" are given particular consideration here: the memory bottleneck and the instruction rate bottleneck. These have been found to force the use of non-trivial solutions in order to achieve faster execution, and many of these only reduce ACET. This section describes the nature of each bottleneck, and successful solutions applied to avoid it. Other bottlenecks (not considered here) include limitations on transistor size, clock frequency and heat dissipation.

#### 2.2.1 The Memory Bottleneck

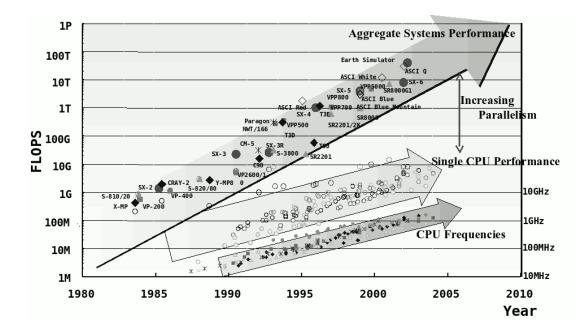

CPU core frequencies increased by many orders of magnitude between the early days of ICs and the time of writing (Figure 2.5). The frequency increases have been enabled by improvements in chip manufacturing technology, allowing smaller transistors to be used.

However, the speed of external connections (particularly to memory devices) has not scaled so

Figure 2.5: The increase in CPU core frequencies from 1980 to 2005. This chart is from [64]. FLOPS is *floating point operations per second*: in this context, this figure is analogous to MIPS.

well. Today (2008), a CPU core may operate at over 2GHz, but the memory bus clock frequency is still limited to around 400MHz. Although these frequencies do not indicate maximum memory *bandwidth* (the amount of data that can be transferred per unit time), minimum memory *latency* (the amount of time required to set up each memory transaction), or the maximum number of instructions that a CPU can execute per unit time, they do reflect the disparity between memory speed and CPU speed in modern computers.

This bottleneck has been well known for some time. It is due to the difficulty of moving data at high speed across a long distance. At very high speeds (e.g. 2GHz), even a few centimetres becomes a problematic distance. The speed of the transfer is affected by the capacitance and impedance of the transmission line, which can result in problematic transmission artifacts such as resonance.

An early solution was separate instruction and data memory, known as a *Harvard architecture*, which doubled the memory access bandwidth and allowed the size of each memory to be tailored to application requirements. This memory arrangement is named after an early implementation in the Harvard Mark I computer [131].

The average performance of memory accesses (and program ACETs) was improved by the invention of the *cache*. A cache memory unit is a small fast memory unit that sits between a CPU and a larger memory bank with slower access (e.g. access via a bus) [99]. It intercepts all memory transactions, and tries to satisfy each without sending any requests to the larger memory bank. This is done by keeping copies of data that recently passed through the cache. Whenever the CPU tries to load data, the address is compared against the addresses of the copies in the cache (called the *tags*). If the requested data is already in cache due to a recent load or store, the copy is supplied without accessing the slow large memory. If it is not in cache, an access to the larger memory is forced.

Caches reduce ACET because programs often repeatedly access the same areas of memory:

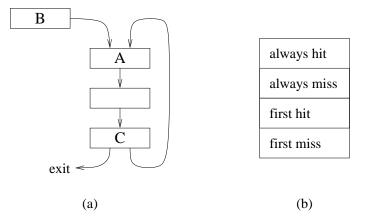

hotspots. However, it is sometimes impossible to know whether instructions or data are in cache or not, and therefore impossible to know how long an access will take. In general, caches provide only *qualified* guarantees about their contents at each position in a program, because cache operations are dependent on the execution history. However, this may still be enough to support a WCET analysis process [183].

Caches are often described as *n*-way associative [195]. In a 1-way associative or *direct-mapped* cache, a real memory address A is mapped onto a line L in a cache of size C by a modulo operation L = mod(A, C). In this arrangement, data at address A will conflict with data at address A + Cand (in general) A + mC for an integer  $m \neq 0$ : i.e. data with address A + mC will disappear from cache as soon as A is accessed. Because C is much smaller than the entire memory of the computer, this situation is common in direct-mapped caches: for example, the machine instructions making up one part of the program can conflict with another part, particularly when function calls are being made. The effect is dependent on addresses assigned to machine code by compiler tools.

To reduce this effect, *multi-way associative* caches are used: *n*-way associative with n > 1. These store *n* pieces of data for each cache line. For example, a 2-way associative cache can store data for address *A* and *A* + *C* on the same line. The chance of a cache conflict is reduced by this scheme, as noted in [44]. An extreme form of the scheme is to make the cache *fully associative*, so C = 1 and *n* is the size of the entire cache. In this scheme, data from any address can be placed anywhere in the cache. The most commonly implemented scheme for selecting a data element for replacement is selection of the *least recently used* (LRU) element [195], but random replacement and "first-in first-out" schemes have also been considered.

Complexity is increased by the process of n-way comparison, and the need to choose an element for replacement whenever a cache miss occurs. This complexity increases hardware costs and energy consumption [139], and it makes WCET analysis more difficult because a more complex model is needed [121]. All of these factors support the argument in favour of simpler direct-mapped caching logic put forward by Hill in [125].

Multi-level caches [99] put several caches in series. These are conventionally assigned a level number to indicate their distance from the CPU. Level zero (L0) is closest to the CPU: this cache is the smallest and fastest of the caches. Other caches (L1, L2, etc.) are progressively larger, slower, physically further from the CPU, and perhaps shared between multiple CPU cores. This hierarchical scheme is an efficient way to minimise slow memory accesses in the average case.

Caches also enable *burst memory accesses*, where more than one item of memory is read at once. Burst memory accesses make more efficient use of high speed bus bandwidth, as the time cost of setup is amortised across a large number of transactions. Burst accesses usually fill an entire *line* of cache - the largest unit for data storage in the cache.

Conventional caches store instructions or data in their original form. A *trace cache* [221, 220] stores the schedule of decoded micro-operations derived from CPU instructions. The micro-operations represent low-level steps to be taken by the CPU to execute each instruction. In some CPUs, such as the Pentium 4 [135], a trace cache allows the reuse of the execution pattern for a particular piece of code. This is particularly useful when that pattern is not just a trivial copy of the original program. For example, the trace cache contents include implicit assumptions about which branches are most likely to be taken.